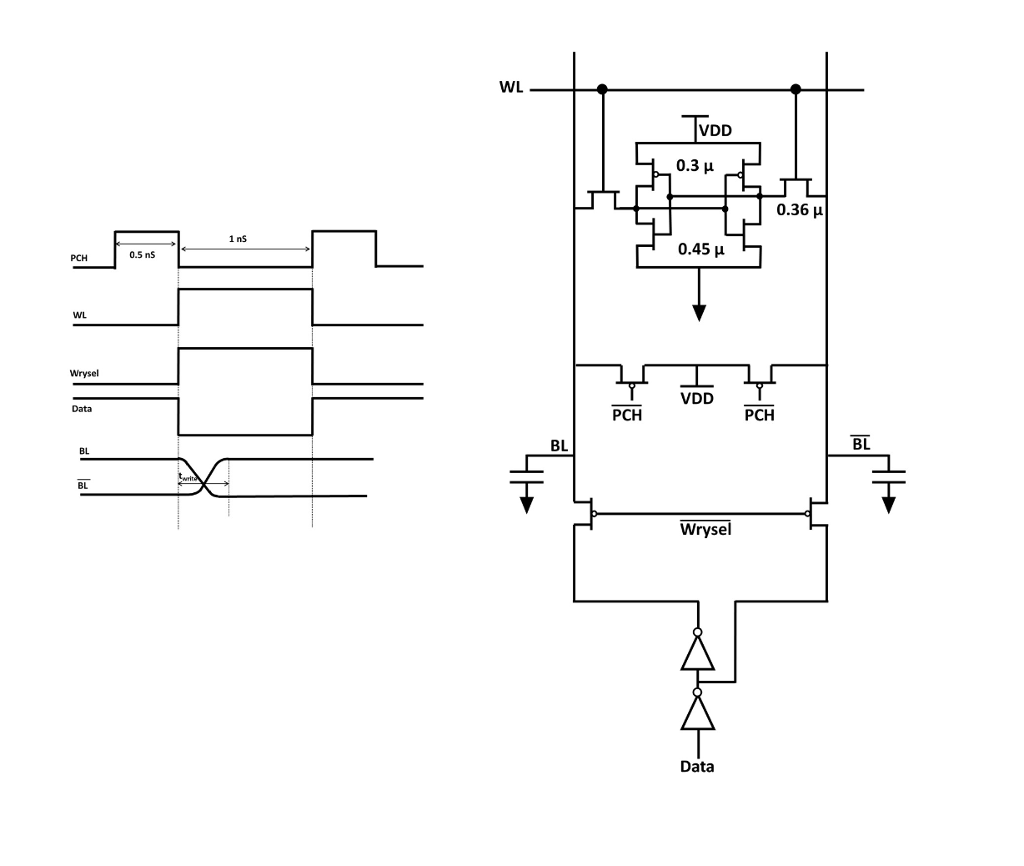

Figure 14 from A Stable 2-Port SRAM Cell Design Against Simultaneously Read/Write-Disturbed Accesses | Semantic Scholar

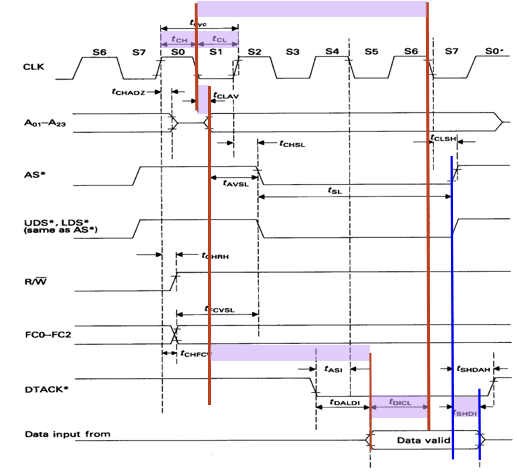

Timing diagrams of 1T-SRAM cell memory operations. The pulse width of... | Download Scientific Diagram

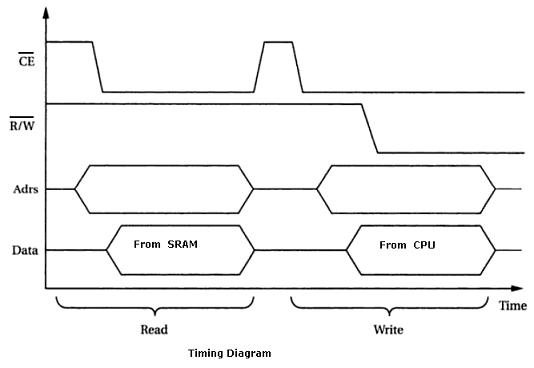

Read protocol of a static RAM: (a) timing diagram, (b) SRAM channel,... | Download Scientific Diagram

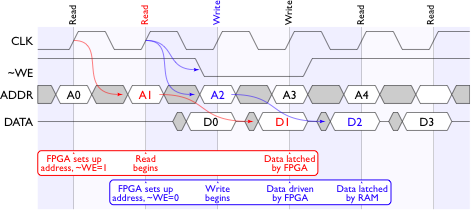

Figure 19 from X-SRAM: Enabling In-Memory Boolean Computations in CMOS Static Random Access Memories | Semantic Scholar